### JOURNAL

#### table of contents

February 1995, Volume 46, Issue 1

#### **Articles**

**Broadband Frequency Characterization of Optical Receivers Using Intensity Noise** by Douglas M. Baney, Wayne B. Soren

**Erbium-Doped Fiber Amplifier Test System** by Edgar Leckel, Jurgen Sang, Rolf Muller, Clemens Ruck, and Christian Hentschel

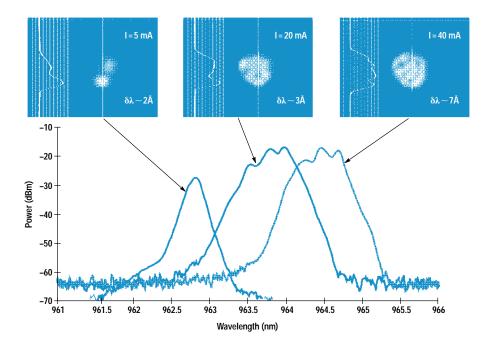

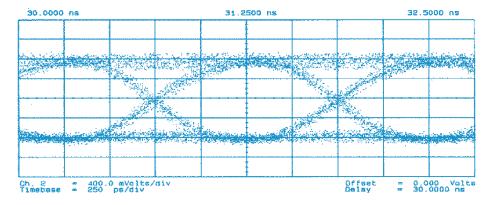

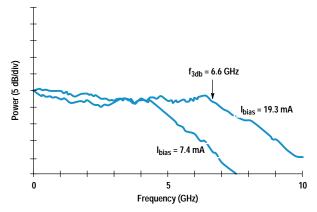

Multi-Quantum-Well Ridge Waveguide Lasers for Tunable External-Cavity Sources

by Tirumala R. Ranganath, Michael J. Ludowise, Patricia A. Beck, Dennis J. Derickson, William H. Perez, Tim L. Bagwell, and David M. Braun

Measurement of Polarization-Mode Dispersion, by Brian L. Heffner and Paul R. Hernday

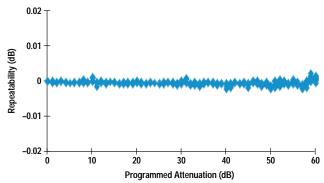

A New Design Approach for a Programmable **Optical Attenuator**

by Siegmar Schmidt and Halmo Fischer

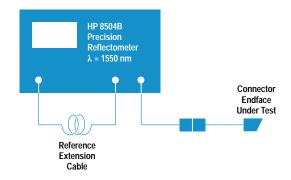

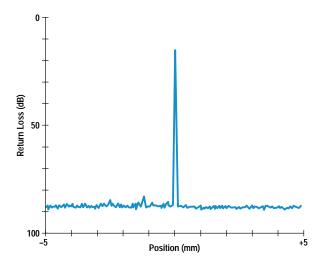

**Precision Reflectometer with Spurious-Free Enhanced Sensitivity,**

by David M. Braun, Dennis J. Derickson, Luis M. Fernandez, and Greg D. LeCheminant

#### High-Power, Low-Internal-Reflection, Edge **Emitting Light-Emitting Diodes**

by Dennis J. Derickson, Patricia A. Beck, Tim L. Bagwell, David M. Braun, Julie E. Fouquet, Forrest G. Kellert, Michael J. Ludowise, William H. Perez, Tirumala R. Ranganath, Gary R. Trott, and Susan R. Sloan

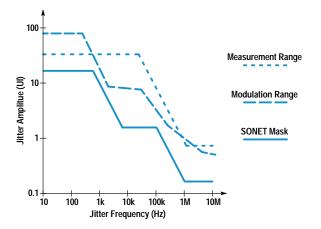

**Jitter Analysis of High-Speed Digital Systems** by Christopher M. Miller and David J. McQuate

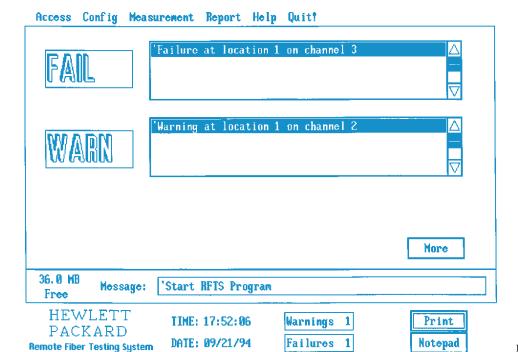

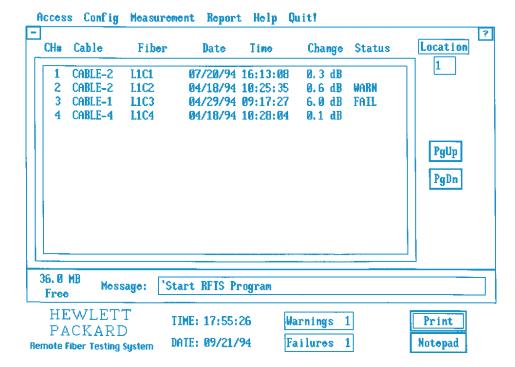

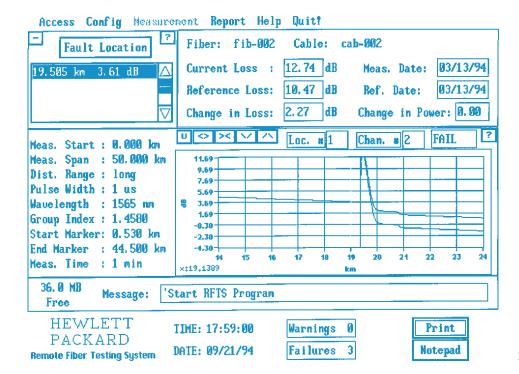

### Automation of Optical Time-Domain Reflectometry Measurements

by Frank A. Maier and Harald Seeger

### **Design and Performance of a Narrowband VCO at 282 THz**

by Peter R. Robrish, Christopher J. Madden, Rory L. VanTuyl, and William R. Trutna, Jr.

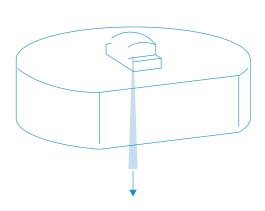

### Surface Emitting Laser for Multimode Data Link Applications

by Michael R.T. Tan, Kenneth H. Hahn, Yu-Min D. Houng, and Shih-Yuan Wang

### Generating Short-Wavelength Light Using a Vertical-Cavity Laser Structure

by Shigeru Nakagawa, Danny E. Mars, and Norihide Yamada

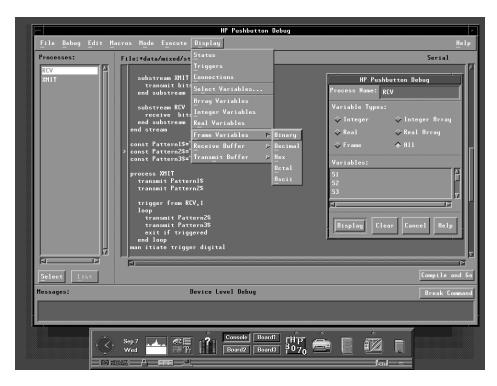

### A New, Flexible Sequencer Architecture for Testing Complex Serial Bit Streams

by Robert E. McAuliffe, James L. Benson, and Christopher B. Cain

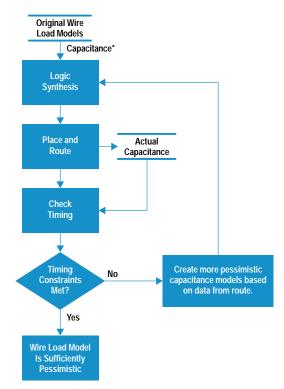

#### Shortening the Time to Volume Production of High-Performance Standard Cell ASICs by Jay D. McDougal and William E. Young

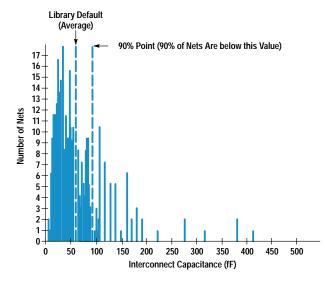

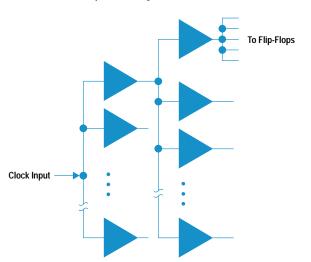

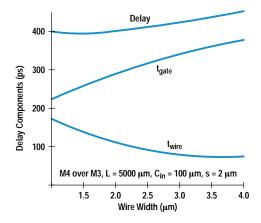

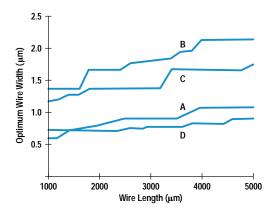

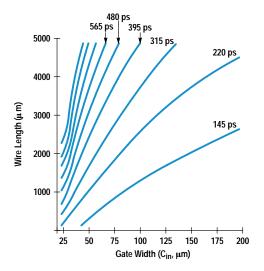

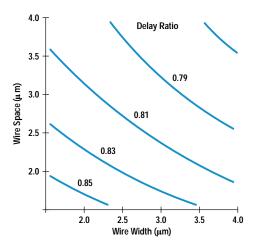

A Framework for Insight into the Impact of Interconnect on 0.35-mm VLSI Performance, by Prasad Raje

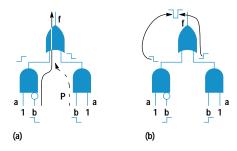

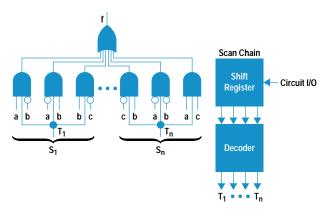

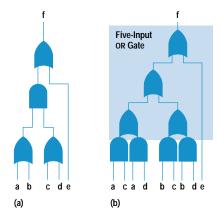

Synthesis of 100% Delay Fault Testable Combinational Circuits by Cube Partitioning by William K. Lam

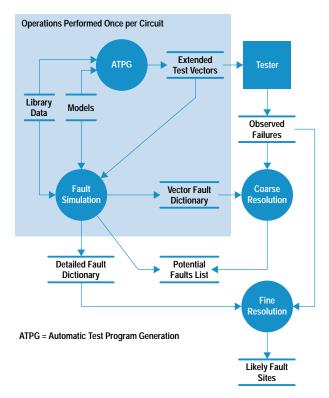

Better Models or Better Algorithms?

Techniques to Improve Fault Diagnosis,

by Robert C. Aitken and Peter C. Maxwell

# Broadband Frequency Characterization of Optical Receivers Using Intensity Noise

Methods for enhancing the dynamic range of the intensity noise technique for high-frequency photoreceiver calibration are proposed and experimentally demonstrated. These methods combine recently developed EDFA\* technology with spectral filtering techniques. The intensity noise calibration technique is portable, easy to use, and field deployable.

#### by Douglas M. Baney and Wayne V. Sorin

Optical technology will play an important role in building the coming information superhighway through its capacity to provide high information throughput and low-loss transmission simultaneously. Optical sources such as semiconductor lasers provide an optical carrier whose intensity is modulated with information to be sent over fiber-optic cable. For high-data-rate communications, lasers typically operate near the 1.55-µm or 1.3-µm low-loss wavelengths in optical fiber. Optical receivers convert the information modulated onto the optical carrier to baseband electrical signals. As demands are made for more information throughput, the bandwidths of optical receivers are increased commensurately.

Accurate characterization of the frequency response of an optical receiver is important to ensure that the receiver is compatible with the data transmission rate. Currently, a number of techniques exist to characterize the frequency response of optical receivers. One method is to compute the Fourier transform from the time-domain impulse response.<sup>1</sup> Frequency domain techniques, such as that used in the HP 8703 lightwave component analyzer, employ frequencyswept sinusoidal modulation of the optical intensity using a high-frequency LiNbO3 modulator. This allows commercially available response measurements from 130 MHz to 20 GHz. The optical heterodyne technique using two Nd-YAG lasers has demonstrated capability from ≈10 MHz to 50 GHz at a wavelength of 1.32 µm. 1,2 These techniques all involve specific trade-offs among frequency coverage, experimental complexity, and sensitivity, and none are completely satisfactory. It is desirable to have the capability to measure the broadband frequency response with a simple rugged optical instrument.

The intensity noise technique offers the possibility of measuring frequency response characteristics of photoreceivers across the entire frequency span of modern electrical spectrum analyzers (for example, 9 kHz to 50 GHz for the HP 8565E). This intensity noise method was first demonstrated using a semiconductor optical amplifier as a source.<sup>3</sup> This technique is of particular interest because the noise exists at all frequencies simultaneously, permitting very rapid optical receiver characterization. Additionally, an unpolarized short-coherence-length optical source is used. This is advantageous

because it makes the measurements immune to polarization drifts and time-varying interference effects from multiple optical reflections, thereby allowing stable, repeatable measurements.

#### **Intensity Noise Techniques**

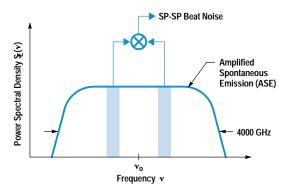

Intensity noise techniques take advantage of the beating between various optical spectral components of a broadbandwidth spontaneous emission source. Any two spectral lines will beat, or mix, to create an intensity fluctuation with a frequency equal to the frequency difference between the two lines. This concept is illustrated in Fig. 1. Since the optical bandwidth of spontaneous emission sources can easily exceed thousands of gigahertz, the intensity beat noise will have a similar frequency content. The fluctuations in optical intensity are referred to as spontaneous-spontaneous, or sp-sp, beat noise.

There are many sources of broad-bandwidth spontaneous emission. Hot surfaces (such as tungsten light bulbs) can provide optical radiation ranging from the visible to the far infrared. Semiconductor sources such as edge emitting light-emitting diodes (EELEDs) provide increased power densities over a wavelength range of about 100 nm. Still higher power densities can be obtained from solid-state sources

\* Erbium-doped fiber amplifier.

**Fig. 1.** Spontaneous-spontaneous (sp-sp) beat noise arising from mixing of the various spectral components from a thermal-like optical noise source.

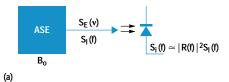

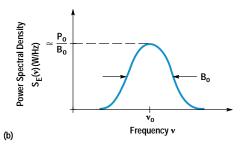

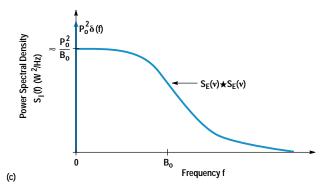

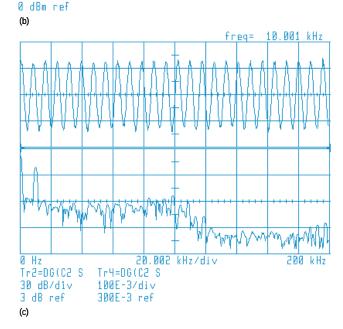

**Fig. 2.** (a) The intensity noise technique for optical receiver calibration. (b) The optical field spectrum as measured on an optical spectrum analyzer. (c) The optical intensity spectrum, which is proportional to the photocurrent spectrum, as measured on an electrical spectrum analyzer.

such as fiber-optic amplifiers (see page 9). The ability to couple these sources of broadband light efficiently into single-mode optical fiber is also important. Coupled power densities can range from about 500 pW/nm for a light bulb to greater than 1 mW/nm for amplified spontaneous emission (ASE) from a fiber-optic amplifier. The high power densities from fiber-optic amplifiers are particularly well-suited for intensity noise generation.

#### Bandpass-Filtered Intensity Noise Technique

Fig. 2 illustrates how the strength and line shape of the optical intensity beat noise are generated from a thermal-like source such as amplified spontaneous emission. Fig. 2a shows the optical power from an ASE source of spectral bandwidth  $B_0$  incident on the high-frequency optical receiver to be tested. The power spectral density of the optical field,  $S_E(v)$ , scaled so that its units are watts/Hz, is commonly used to characterize the output of optical sources. This quantity is typically measured using an optical spectrum analyzer. Fig. 2b shows a typical spectrum for  $S_E(v)$  with full width at half maximum bandwidth  $B_0$  and center frequency  $v_0$ . The average optical power  $P_0$  is found by integrating over the optical spectrum, that is,

$$P_{O} = \int_{0}^{\infty} S_{E}(v) dv,$$

which gives a peak value for the spectral density of approximately  $P_{\rm O}/B_{\rm o}$ . It should be noted that all power spectral densities discussed in this paper are single-sided, with energy only at positive frequencies.

Since photodiode current is proportional to optical intensity and not electric field, a more relevant quantity to consider is the power spectral density of the optical intensity,  $S_I(f)$ , which is scaled to have units of watts<sup>2</sup>/Hz. This quantity is related to the optical field spectrum by the relatively simple expression:

$$S_{I}(f) = P_{O}^{2} \delta(f) + S_{E}(v) \star S_{E}(v), \tag{1}$$

where  $\delta(f)$  represents a delta function and  $\star$  denotes the single-sided autocorrelation (integrated over positive frequencies). This result assumes unpolarized ASE and singlesided power spectral densities. This expression is valid for optical radiation with thermal-like noise statistics, such as amplified spontaneous emission. The effects of shot noise are not included in equation 1 because it is easier to account for this noise after the optical intensity is converted to a photocurrent. The result of equation 1 is graphically illustrated in Fig. 2c. Intensity beat noise exists up to frequencies determined by the spectral width of the ASE source. These frequencies are typically on the order of thousands of gigahertz. The magnitude of the beat noise at low frequencies is approximately  $P_0^2/B_0$ , the exact value depending on the line shape of the electric field spectrum. More accurate values for typically encountered line shapes are given later.

The power spectral density of the detected photocurrent,  $S_i(f)$ , in units of amperes<sup>2</sup>/Hz, equals that of the incoming intensity spectrum except for the filtering effects of the photodiode. If the frequency dependent responsivity (i.e., transfer function) for the photodiode is given by R(f), which has units of amperes/watt, then the photocurrent spectrum can be expressed as:

$$S_{i}(f) \simeq |R(f)|^{2}S_{I}(f) \tag{2}$$

The receiver thermal and shot noises are not included in equation 2. The value for these two noise sources will determine the SNR (signal-to-noise ratio) for the measurement technique. Assuming that the optical beat noise signal is larger than the shot or thermal noise, this expression can be used to determine the magnitude |R(f)| of the frequency response of the photodiode. This measurement is performed by observing the photocurrent spectrum  $S_i(f)$  with an electrical spectrum analyzer. If the spectral width of the ASE source,  $B_o$ , is much larger than the frequency response of the photodiode, then  $S_I(f)$  can be assumed constant, and the responsivity squared  $|R(f)|^2$  of the photodiode is displayed directly on the electrical spectrum analyzer.

One previous difficulty in the practical use of this detector calibration technique is the small value for the intensity beat noise provided by typical ASE sources. This has presented a problem for high-frequency calibration because the thermal noise level associated with wideband receivers is typically quite large. In this paper we show that by combining the recent development of erbium-doped fiber amplifiers with spectral filtering techniques, we can overcome the previous limitation of small signal strength.

To understand how to optimize the ASE for detector calibration, the concept of relative intensity noise or RIN, which has units of  $\rm Hz^{-1}$ , will be introduced. This parameter can be thought of as the fractional intensity noise associated with an optical source. The definition for RIN in terms of the optical intensity spectrum is:

$$RIN(f) = S_I(f)/P_O^2.$$

(3)

Thus RIN is the spectral density of the optical intensity at a given frequency divided by its integrated value at zero frequency. An equivalent definition equates RIN to the variance of the optical intensity  $\langle \Delta I^2(f) \rangle$  in a one-hertz bandwidth divided by the average intensity squared. Since the optical bandwidth  $B_o$  is usually much larger than the electrical detection bandwidth, the RIN from an ASE source is usually considered to be constant, equal to its low-frequency value. From Fig. 2c, it can be seen that this value is approximately given by:

$$RIN \simeq 1/B_0. \tag{4}$$

This result is valid for unpolarized light with thermal-like noise statistics. A more accurate value for equation 4 requires knowledge of the line shape of the ASE spectrum.

Normally, for a given source, one would increase the average optical power incident onto a photoreceiver to increase the photocurrent beat noise and hence the measurement sensitivity. With the development of EDFAs (erbium-doped fiber amplifiers), the average optical powers attainable will easily saturate high-frequency photoreceivers. This means increasing optical power is no longer an issue, and for a given optical receiver, a power just below its saturation level should be used for calibration purposes. Since incident optical power can now be considered a constant, depending on the detector saturation level, the concept of RIN becomes useful because increasing its value increases the SNR of the intensity noise technique. According to equation 4, this means that decreasing the spectral width Bo of the ASE source will improve the SNR for detector calibration. The only limitation is that eventually there will be a roll-off in the high-frequency content of the beat noise.

#### Effects of Line Shape and Bandwidth

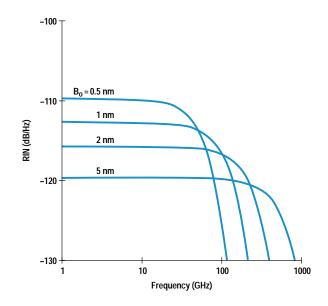

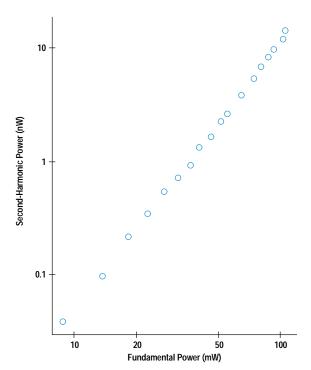

As the optical bandwidth is reduced, the maximum frequency separation of beating components also decreases. In Fig. 3, the RIN is shown as a function of frequency for four

Fig. 3. Relative intensity noise (RIN) for a Gaussian-shaped optical field power spectrum centered at 1.55  $\mu m$ .

different optical bandwidths. The plotted curves correspond to the case of an unpolarized ASE source with a Gaussian optical spectral shape. The highest RIN is achieved at the lowest frequencies with the narrowest optical bandwidth. At frequencies comparable to the optical spectral bandwidth, roll-off in the RIN becomes apparent. The RIN for the 5-nm spectral width is relatively constant to several hundred gigahertz. Expressions for RIN as a function of frequency are shown in Table I for the case of Lorentzian, Gaussian, and rectangular optical field spectrums. The Lorentzian shape corresponds closely to the spectrum of commonly used Fabry-Perot optical filters. The Gaussian spectrum is sometimes used to describe the spectra of EELEDs or lasers operating below threshold. The rectangle function approximates some interference filters, grating-based monochromators, and chirped fiber gratings. The normalized (to unity) optical field spectrum is also included in Table I for reference. The line width Bo in each case is the FWHM (full width at half maximum) of the optical field spectrum.

Comparing the low-frequency RIN values for each of the different spectral shapes, the rectangle spectrum delivers the most RIN  $(1/B_0)$ , followed by the Gaussian  $(0.66/B_0)$ ,

### Table I Relationship between Unpolarized Optical Field Spectrum and RIN

<sup>\*</sup>  $\sqcap$  = rectangle function.  $\land$  = triangle function.

#### 1.55-µm Fiber-Optic Amplifier

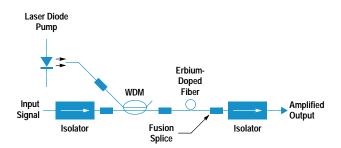

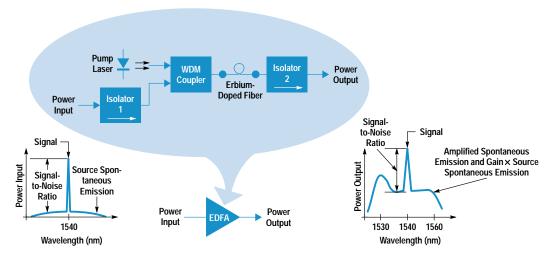

The fiber-optic amplifier is a key element in modern high-data-rate communications. Its large optical bandwidth, ≈ 4000 gigahertz, makes it effectively transparent to data rate and format changes, allowing system upgrades without modifications to the amplifier itself. The most prevalent fiber-optic amplifier is called the erbiumdoped fiber amplifier (EDFA). It provides amplification in the third telecommunications window centered at a wavelength of 1.55  $\mu m$ . The EDFA has four essential components, as shown in Fig. 1. These are the laser diode pump, the wavelength division multiplexer (WDM), the erbium-doped optical fiber, and the optical isolators. To achieve optical amplification, it is necessary to excite the erbium ions situated in the fiber core from their ground state to a higher-energy metastable state. A diagram of the relevant erbium ion energy states is shown in Fig. 2. The erbium ions are excited by coupling pump light (≈20 mW or greater) through the WDM into the erbium-doped fiber. Commonly used pump wavelengths are 980 nm and 1480 nm. The ions absorb the pump light and are excited to their metastable state. Once the ions are in this state, they return to the ground state either by stimulated emission or, after about 10 ms, through spontaneous emission. Light to be amplified passes through the input isolator and WDM and arrives at the excited erbium ions distributed along the optical fiber core. Stimulated emission occurs, resulting in additional photons that are indistinguishable from the input photons. Thus, amplification is achieved. Optical isolators shield the amplifier from reflections that may cause lasing or the generation of excess amplified spontaneous emissions (ASE).

Good EDFA design typically requires reduction of optical losses at the amplifier input and minimizing optical reflections within the amplifier. EDFAs with greater than 30-dB optical gain, more than 10-mW output power, and less than 5-dB noise figure are readily achieved in practice.

Fig. 1. Schematic of an erbium-doped fiber amplifier showing essential optical components. The WDM is a wavelength division multiplexer.

<sup>2</sup>H<sub>11/2</sub> Green 4S3/2 540 nm 670 nm 4F<sub>9/2</sub> 820 nm 4l<sub>9/2</sub> 980 nm  $^{4}I_{11/2}$ 1480 nm 10 ms 4I<sub>13/2</sub> Metastable State 1550 nm Ground 4I<sub>15/2</sub> State

Fig. 2. Relevant erbium ion energy levels.

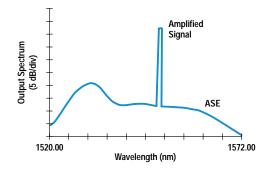

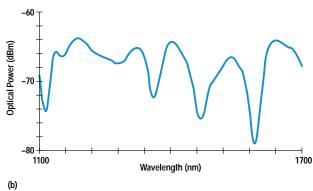

ASE is generated in optical amplifiers when excited ions spontaneously decay to the ground state. The spontaneously emitted photons, if guided by the optical fiber, will subsequently be amplified (by the excited ions) as they propagate along the fiber. This can result in substantial ASE powers (> 10 mW) at the amplifier output. A typical spectrum of signal and ASE at the amplifier output is shown in Fig. 3. The ASE can extend over a broad spectral range, in this case in excess of 40 nm.

$\label{eq:Fig.3.} \textbf{Spectrum of amplified spontaneous emissions (ASE) and amplified signal at the amplifier output.}$

and next by the Lorentzian (0.32/B<sub>0</sub>). If the ASE source is polarized, the RIN will be twice as large for all three cases.

If the optical receiver response measurements are performed in the flat RIN regime (see Fig. 3), no specific knowledge of the source line shape is required. However, if the spectral line shape for the ASE source is accurately characterized, additional measurement sensitivity can be obtained by using narrower optical filters and correcting for the roll-off in the response data.

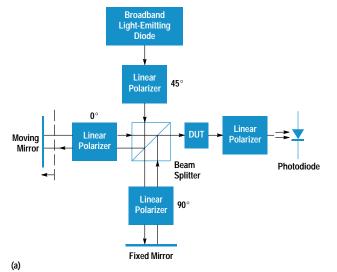

### Experiment: Intensity Noise Technique Using Optical Bandwidth Reduction

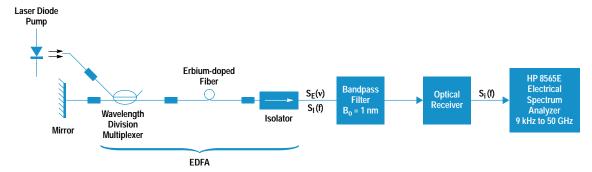

To demonstrate the filtered intensity noise technique, measurements were performed at a wavelength of 1.55 µm on a SONET receiver with 1-GHz electrical bandwidth. The measurement setup is shown in Fig. 4. The mirror at the end of the EDFA results in two-pass ASE generation. This doubly amplified ASE is then filtered by an optical bandpass filter with a 1-nm spectral width. All optical connections were fusion-spliced to eliminate optical reflections. The presence

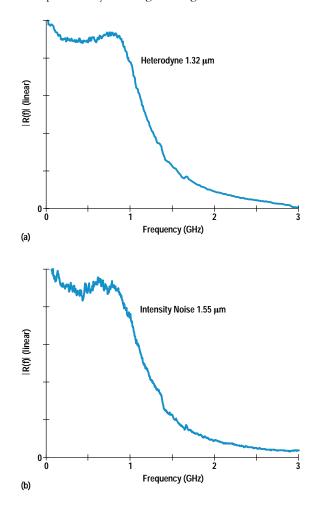

of multiple optical reflections could impart undesirable intensity ripple onto an otherwise constant RIN spectrum, which would be difficult to separate from the receiver frequency response. The bandpass filtering resulted in approximately a 15-dB improvement in SNR. An average optical power of 200  $\mu W$  was incident onto the receiver; this was below its saturation level of 320  $\mu W$ . Using a more complicated dual Nd-YAG optical heterodyne system, measurements at a wavelength of 1.32  $\mu m$  were performed for comparison with the intensity noise technique. The intensity noise technique shows excellent agreement when compared with the standard heterodyne method as indicated in Fig. 5.

#### **Periodically Filtered Intensity Noise Technique**

As discussed earlier, for a fixed average optical power, the spontaneous-spontaneous beat noise in the photocurrent spectrum increases as the optical bandwidth  $B_{\rm o}$  is reduced. This increase in signal strength is desirable, but if the optical bandwidth is reduced too much, the high-frequency content of the beat noise will start to roll off, making it unsuitable

Fig. 4. Experimental arrangement for frequency response measurement of a SONET photoreceiver using the bandpass-filtered intensity noise technique.

for high-frequency detector calibration. In practice, this trade-off between signal strength and frequency content becomes a problem when trying to characterize high-frequency, low-gain optical receivers. Because of the large input noise figures (typically 30 dB) associated with high-frequency electrical spectrum analyzers, large values of photocurrent beat noise are required.

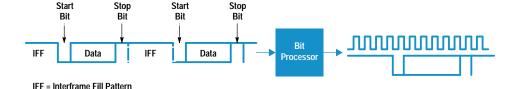

The periodically filtered intensity noise technique solves this trade-off problem by allowing the magnitude of the beat

**Fig. 5.** Measurement of a SONET receiver frequency response using (a) a 1.32- $\mu$ m Nd-YAG optical heterodyne system and (b) the 1.55- $\mu$ m filtered intensity noise technique.

noise to be increased without loss of its high-frequency content. This is accomplished by passing the amplified spontaneous emission through a Fabry-Perot filter and then on to the high-frequency optical receiver. This reduces the average optical power while maintaining the magnitude of the spontaneous-spontaneous beat noise at periodic frequencies spaced at intervals equal to the free spectral range of the filter. The result is an increase in RIN at periodically spaced beat frequencies. If needed, optical amplification can then be used to boost the average optical power to a value just under the saturation level for the receiver.

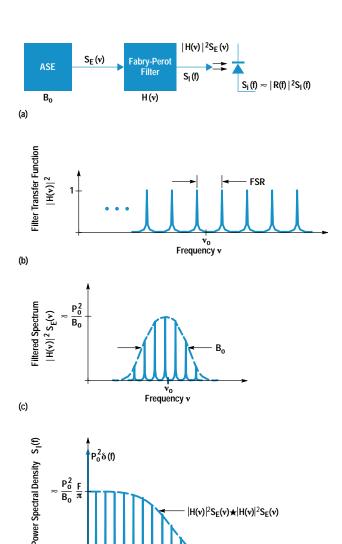

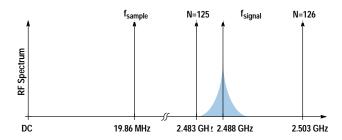

Details of the periodically filtered technique are shown in Fig. 6. Fig. 6a shows the ASE from a source such as an erbium-doped fiber amplifier passing through a Fabry-Perot filter and on to the test optical receiver. The transmission characteristics of the Fabry-Perot filter are determined by its free spectral range, FSR, and its finesse, F. FSR is the frequency separation of the transmission maxima and F is the ratio of the FSR to the width of the transmission maxima. From a signal processing point of view, the Fabry-Perot filter has a frequency-domain transfer function for the optical field given by H(v). The squared magnitude of this transfer function is illustrated in Fig. 6b. For the ideal case, the transmission through the filter would be unity at frequencies separated by the FSR. After passing through the filter, the power spectral density of the input optical field  $S_E(v)$  will be transformed to  $|H(v)|^2S_E(v)$ . Fig. 6c shows the filtered spectrum, which is incident on the optical receiver. Strong beat signals occur in the intensity separated by frequency intervals equal to the FSR of the Fabry-Perot filter. As described earlier in equation 1, the power spectral density for the optical intensity  $S_{I}(f)$  can be obtained from an autocorrelation of the input electric field spectrum:

$$S_{I}(f) \simeq P_{o}^{2}\delta(f) + |H(v)|^{2}S_{E}(v) \star |H(v)|^{2}S_{E}(v).$$

(5)

This expression is valid for unpolarized amplified spontaneous emission (see equation 1). The result of equation 5 is illustrated in Fig. 6d. Intensity noise peaks are evident at frequency locations separated by the FSR of the Fabry-Perot filter. Relative to the dc signal, these peaks are a factor of  $F/\pi$  larger than the unfiltered case shown in Fig. 2c. For a typical finesse of F=100, this corresponds to an increase in signal-to-noise ratio of about 15 dB for photodiode characterization. The penalty for the increased SNR is that beat signals only occur at specific frequencies. This constraint is not very severe because this frequency spacing can be set to any

**Fig. 6.** (a) Block diagram illustrating the periodically filtered intensity noise calibration technique. (b) Transfer function of the Fabry-Perot filter. (c) Optical field spectrum incident at the photoreceiver. (d) Photocurrent spectrum as measured on an electrical spectrum analyzer.

Frequency f

desired value by proper choice of the filter FSR. As described earlier, the optical receiver frequency response can be obtained using equation 2, which relates the optical intensity spectrum to the photocurrent spectrum measured using an electrical spectrum analyzer. Assuming an optical bandwidth  $B_{\rm O}$  much larger than the frequency response of the optical receiver, the photocurrent power spectrum is given by:

$$S_{i}(f) \simeq \left| \left| R(f) \right|^{2} S_{I}(f) = \left| \left| R(f) \right|^{2} \frac{P_{O}^{2}}{B_{O}} \cdot \frac{F}{\pi} \sum_{k} \frac{1}{1 + \left( \frac{f - kFSR}{\Delta v} \right)^{2}}$$

where  $\Delta v$  is the spectral width of the Fabry-Perot filter and is given by  $\Delta v$  = FSR/F. This result illustrates that the magnitude of the photocurrent beat signal can be increased relative to a fixed average current without sacrificing its high-frequency content.

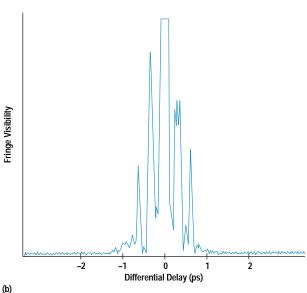

### **Experiment: Intensity Noise Technique Using Periodic Bandwidth Reduction**

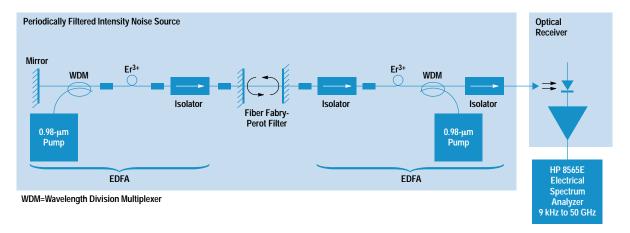

To demonstrate the above result, the arrangement illustrated in Fig. 7 was used. The ASE obtained from the two-pass EDFA superfluorescent source generated an optical signal with a spectral width of about 40 nm centered at 1.55 μm. This ASE then passed through an optical isolator, which prevented the two-pass superfluorescent source from becoming a laser. The output of the isolator was then sent through a single-mode fiber Fabry-Perot filter with finesse F = 80 and free spectral range FSR = 680 MHz. To boost the average power, the filter output was optically amplified by a final EDFA postamplifier. Average output powers of several milliwatts can be obtained using this arrangement. Fusion splices between the superfluorescent source, the filter and the postamplifier were used to minimize reflections. This is important because multiple reflections will add amplitude ripple to the intensity power spectrum. The photoreceiver consisted of a high-speed 14-µm-diameter, InGaAs p-i-n photodiode followed by a traveling wave GaAs microwave amplifier. A 50-GHz electrical spectrum analyzer (HP 8565E) displayed the photocurrent power spectrum.

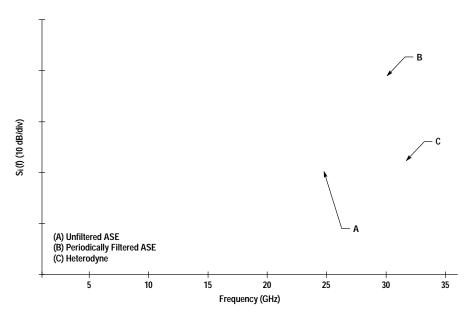

For comparison purposes, three different techniques were used to measure the frequency response of the photoreceiver. The results of these three measurements are shown in Fig. 8. The curve labeled A was obtained using unfiltered ASE. For

Fig. 7. Experimental setup used to demonstrate the periodically filtered intensity noise technique.

(d)

**Fig. 8.** Frequency response measurements of a high-frequency optical receiver using three techniques. The intensity noise curves were measured at 1.55  $\mu$ m and the heterodyne measurement was made at 1.32  $\mu$ m.

curve B, the periodically filtered ASE output was used. The average optical powers were held constant and equal for curves A and B. Curve C was generated using an optical heterodyne technique. Curves A and B experimentally demonstrate an SNR enhancement of approximately 17 dB between the filtered and unfiltered intensity noise techniques. Comparison between the heterodyne technique and the two intensity noise techniques shows very good agreement, illustrating the flat intensity noise spectrum obtained from the EDFA noise source.

#### Discussion

The use of a broadband intensity noise source for high-frequency detector calibration has several advantages over other frequency-domain techniques. One important advantage is that calibration of the frequency response of the optical source is not necessary since it can be made flat by choosing the ASE spectral width to be much larger than the frequency response of the photodetector. This is not the case for other frequency-domain techniques. For example, sinusoidal intensity modulation of an optical source using a LiNbO<sub>3</sub> modulator requires careful calibration of the frequency response of the modulator, which becomes increasingly difficult at high frequencies. Any errors in this calibration are passed on to the detector's frequency response.

Compared with heterodyne techniques, the intensity technique is rugged and field deployable and does not require stable polarization alignment. Since the intensity noise is present at all frequencies, it allows rapid measurements. Additionally, the long coherence length of laser sources in the presence of optical reflections makes the heterodyne measurement more susceptible to environmental effects.

The intensity noise method also has advantages compared to time-domain impulse measurement methods. For high-frequency measurements, the effects of the oscilloscope must be deconvolved from the measurement before an accurate calibration can be obtained. This can often be arduous since accurate impulse responses for high-frequency oscilloscopes are difficult to obtain. The advantage of not requiring careful

source calibration for the intensity noise technique is an important consideration in developing a portable, low-cost, user-friendly calibration technique.

#### **Summary**

In this paper we have proposed and experimentally demonstrated methods for enhancing the dynamic range of the intensity noise technique for high-frequency photoreceiver calibration. By combining recently developed EDFA technology with spectral filtering techniques, we have shown that the magnitude of intensity beat noise can be increased to values practical for unamplified photodiode calibration. Using the periodically filtered technique, RIN values larger than -100 dB/Hz can be achieved over a frequency range in excess of 100 GHz. The intensity noise calibration technique has the potential for becoming a portable, easy to use, field deployable calibration method.

#### Acknowledgments

Mike McClendon and Chris Madden performed the optical heterodyne measurements and Mohammad Shakouri provided the 30-GHz photoreceiver. Steve Newton provided important support for this project.

#### References

- 1. D.J. McQuate, K.W. Chang, and C.J. Madden, "Calibration of Lightwave Detectors to 50 GHz," *Hewlett-Packard Journal*, Vol. 44, no. 1, February 1993, pp. 87-91.

- 2. S. Kawanishi, A. Takada, and M. Saruwatari, "Wideband Frequency-Response Measurement of Optical Receivers Using Optical Heterodyne Detection," *Journal of Lightwave Technology*, Vol. 7, no. 1, 1989, pp. 92-98.

- 3. E. Eichen, J. Schlafer, W. Rideout, and J. McCabe, "Wide-Bandwidth Receiver/Photodetector Frequency Response Measurements Using Amplified Spontaneous Emission from a Semiconductor Optical Amplifier," *Journal of Lightwave Technology*, Vol. 8, no. 6, 1990, pp. 912-916.

- 4. D.M. Baney, W.V. Sorin, and S.A. Newton, "High-Frequency Photodiode Characterization Using a Filtered Intensity Noise Technique," *IEEE Photonics Technology Letters*, Vol. 6, no. 10, October 1994, pp. 1258-1260.

### Erbium-Doped Fiber Amplifier Test System

The HP 81600 Series 200 EDFA test system combines various instruments with powerful software to characterize erbium-doped fiber amplifiers. The system is a turnkey solution with fully specified uncertainty.

#### by Edgar Leckel, Jürgen Sang, Rolf Müller, Clemens Rück, and Christian Hentschel

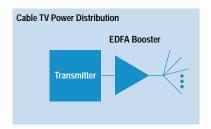

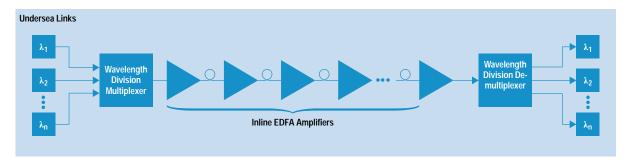

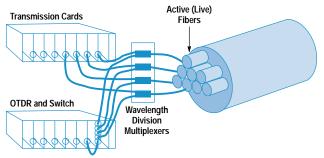

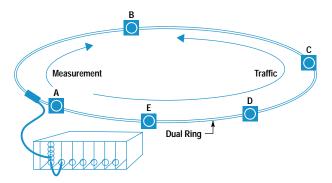

Erbium-doped amplifiers (EDFAs) are the latest state-of-the-art solution for amplifying optical signals in lightwave transmission systems (see Fig. 1). They are used as booster amplifiers on the transmitter side to get as much power as possible into the link, as inline amplifiers to overcome the loss of the fiber, and as preamplifiers at the receiver end to boost signals to the necessary receiver levels. EDFAs can be used in single-wavelength transmission systems, in wavelength division multiplexed (WDM) systems, and in soliton transmission systems. To use EDFAs in the various applications it is necessary to characterize the single amplifier as a component.

#### **Parameters and Measurement Techniques**

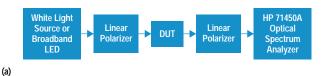

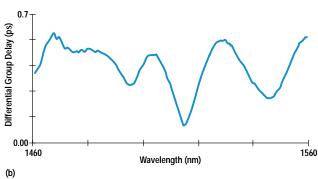

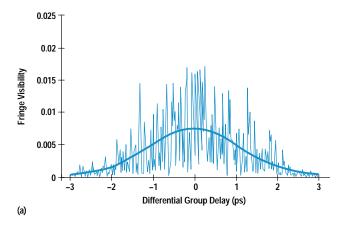

The main parameters describing an EDFA are signal output power, total output power, gain, and noise figure. All of these parameters are dependent on input power level and wavelength. To characterize these amplifiers fully it is necessary to measure their dependence on both input power and wavelength (see Fig. 2).

Signal output power is measured with an optical spectrum analyzer and the total output power is measured with a

power meter. The gain is the ratio of the signal output power of the amplifier to the signal input power.

Noise figure is defined as the ratio of the signal-to-noise ratio at the input to the signal-to-noise ratio at the output of the amplifier under the following conditions: shot-noise-limited photodetector, shot-noise-limited input signal, and optical bandwidth approaching zero. The main problem in measuring the noise figure is that sources used for generating variable input power and wavelength also generate a broad LED-like spectrum called source spontaneous emission (SSE). The SSE is amplified and adds to the output power. The amplifier output consists of amplified signal and amplified spontaneous emission (ASE). To measure only the signal and ASE contribution from the amplifier we have to eliminate the contribution from the SSE.

There are two principal methods<sup>2</sup> for measuring the exact noise level of the amplifier. The first is called the amplified spontaneous emission interpolation subtraction method. In this method the SSE level of the laser source is determined during the calibration and stored in a calibration file. With this calibration and the measured gain, the SSE  $\times$  gain

Fig. 1. Erbium-doped fiber amplifier (EDFA) applications in communication systems.

Fig. 2. Key components, optical signals, and measurement parameters for EDFA characterization.

contribution can be subtracted from the total spontaneous power level to obtain the ASE level of the amplifier itself.

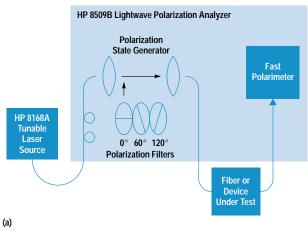

The second method is called the polarization extinction method. It depends on the fact that the signal and the SSE of the laser source have the same state of polarization because there is a polarizer at the output of the tunable laser signal source. The amplifier's ASE is unpolarized. This makes it possible to extinguish the amplified SSE contribution by blocking the signal and therefore also the SSE contribution after the amplifier. The extinction is accomplished with a polarization controller/filter.

#### **EDFA Test System**

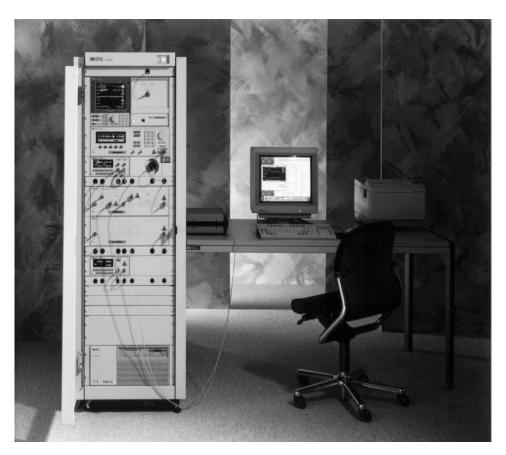

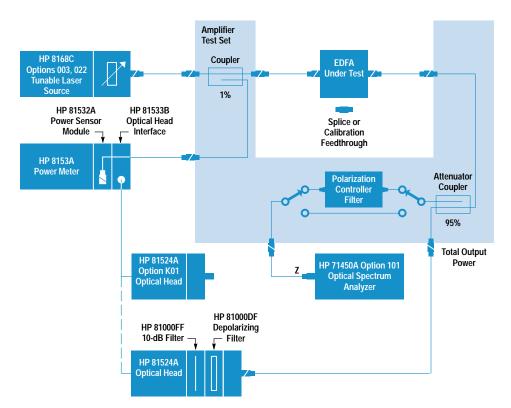

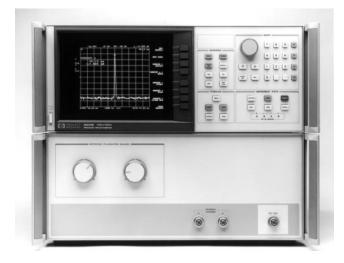

The HP 81600 Series 200 EDFA test system is shown in Fig. 3. Fig. 4 is its block diagram. The tunable laser source with built-in attenuator<sup>3</sup> provides the input power levels over the required wavelength range. To guarantee the absolute power level at the input of the EDFA, the power is monitored by means of a coupler and a calibrated power meter.<sup>4</sup> At the output of the EDFA the total output power is measured with a 5% tap and a power meter. Because of the high output power of the EDFA it is necessary to insert attenuators in front of the power meter heads. The coupler for the power

**Fig. 3.** HP 81600 Series 200 EDFA test system.

**Fig. 4.** Block diagram of the HP 81600 Series 200 EDFA test system.

meter acts as an attenuator for the optical spectrum analyzer. The coupler is followed by a switch and the polarization controller/filter arrangement. This makes it possible to measure the signal directly or via the polarization controller/filter with the polarization extinction method. The optical spectrum analyzer acts as a wavelength-selective power measurement device.

#### **Amplifier Test Set**

A specially developed instrument for this test system is the amplifier test set. The amplifier test set consists of couplers for monitoring the input and output power of the EDFA and a polarization controller/filter. The switches are used to select between gain measurement on the straight path and ASE measurement on the polarization controller/filter path.

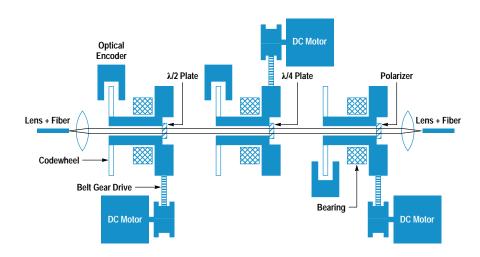

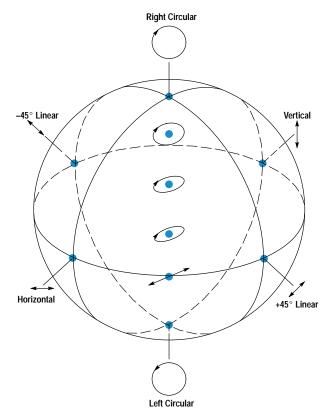

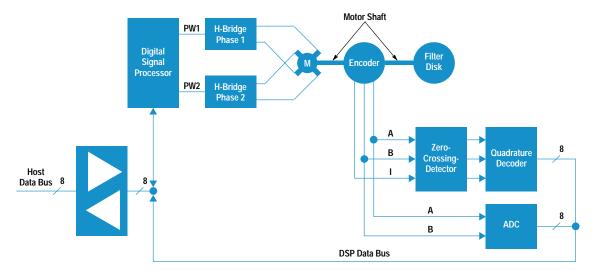

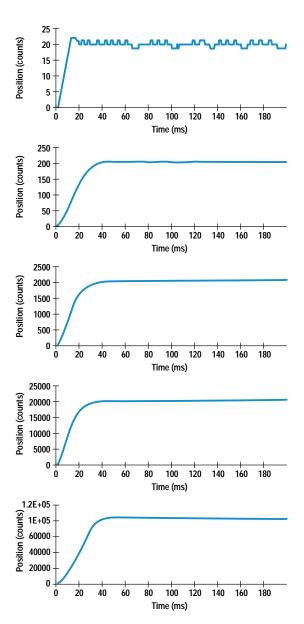

The optical design of the polarization controller/filter is based on two retardation plates—one quarter-wave and one half-wave plate—and a linear dichroic polarizer (see Fig. 5). These parts are mounted on rotatable hollow shafts so that

the collimated light beam can pass through the shafts and through the center of the optical codewheel. The whole assembly—optical parts and encoder—is driven by a dc motor coupled with a belt gear drive. With this design any incoming state of polarization can be transformed into any other state by rotating the retardation plates to defined angular positions. A polarizer is added at the output so that linear states of polarization can be extinguished.

In the polarization extinction method the polarization controller/filter is used as a polarization analyzer to determine the input state of polarization. Based on this measurement, the retardation plates are rotated to calculated angular positions, which change the signal and the amplified SSE to a linear state perpendicular to the pass direction of the polarizer. This causes the signal and the amplified SSE to be extinguished.

The amplifier test set contributes to the overall system uncertainty. Therefore, the couplers, switches, and polarization

**Fig. 5.** Polarization controller/filter.

controller/filter were designed or selected for lowest polarization dependent loss. In addition, the switches were selected for very good repeatability and high return loss. The polarization controller/filter was also designed for low rotation dependent loss. Finally, an intelligent algorithm and optimized speed of the polarization controller/filter reduce the total measurement time.

Before starting a measurement, it is necessary to run a calibration. The first calibration step is to measure the coupling ratio of the coupler before the DUT with the help of the two power meter heads. The second step is to calibrate the optical spectrum analyzer and the power meter in conjunction with the attenuators and the losses of the paths. A feed-through is used to connect the test system's input and output ports. The calibration is verified by measuring the feed-through. In this case the gain is well-known (0 dB) and the output power must be the same as the input power.

#### **EDFA Test System Uncertainty**

Major efforts went into understanding, characterizing and, wherever possible, correcting the actual and potential sources of error in the HP 81600 Series 200 EDFA test system. This task is complex because the test system and measurement tasks are complex. All measurement tasks start with the calibration of the system, in which optical power traceability to PTB and NIST is ensured. Optical power traceability is important in conjunction with the signal power, total power, and ASE measurements, the latter being used to calculated the noise figure. For the gain measurement, it is important that the power scale be linear. This parameter is also traceable to PTB through a chain of scale comparisons. Finally, wavelength traceability is ensured through comparisons to specific gas lamps and lasers, which can be considered natural physical constants.

A careful uncertainty analysis was carried out for each of four parameters: signal power, total power, gain, and noise figure. In each case, the entire process of calculation was analyzed. For example, the gain is defined as the ratio of signal output power to signal input power. Signal input power is measured by means of the input coupler and the HP 8153A optical power meter with the HP 81532A power sensor module. This measurement relies on the accuracy of the input calibration and the performance of the equipment involved. Signal output power is measured with the amplifier test set and an optical spectrum analyzer. This measurement relies on the accuracy of the output calibration and on the performance of the equipment.

As an example, the following represents a summary of the uncertainty analysis for the determination of noise figure. This analysis is the most complicated because the noise figure F is a function of the ASE power density  $\rho_{ase}$  and the gain G:

$$F = \frac{1}{G} + \frac{\rho_{ase}}{h\nu G}$$

.

where h is Planck's constant and  $\nu$  is the optical frequency. Analyzing this equation for the origin of the numeric values and the performance of the instruments involved leads to the following list of partial uncertainties for the noise figure:

Polarization dependence of the amplifier test set and the optical spectrum analyzer

- Small errors in the optical spectrum analyzer scale fidelity

- Drift effects in the amplifier test set

- Uncertainty attributable to the input connector pair (the output connector pair cancels out because it influences the gain and the ASE in the same way)

- Calibration uncertainty of the HP 81524A optical head

- Finite accuracy of the cancellation of the source's spontaneous emission in determining the ASE level

- Loss uncertainty of the path through the polarization controller

- Uncertainty of the optical spectrum analyzer's resolution bandwidth

- Uncertainty of the input power measurement resulting from the polarization dependence of the input coupler and the HP 81532A power sensor module.

Table I shows a summary of the uncertainty analysis for the HP 81600 Series 200 EDFA test system in conjunction with the polarization extinction technique. Also shown are the total uncertainties, which are obtained by root-sum-squaring. They serve as the basis for the test system specifications.

### Table I Uncertainty Summary for HP 81600 Series 200 EDFA Test System

| Uncertainty                                          |                       | Output<br>Signal<br>(dB) | Gain<br>(dB)   | Noise<br>Figure<br>(dB) |

|------------------------------------------------------|-----------------------|--------------------------|----------------|-------------------------|

| Gain Compression by SSE                              |                       | ±0.10                    | ±0.10          |                         |

| Optical Spectrum Analyzer<br>Polarization Dependence |                       | ±0.10                    | ±0.10          | ±0.05                   |

| Test Set Polarization<br>Dependence                  |                       | ±0.07                    | ±0.07          | ±0.07                   |

| Optical Spectrum Analyzer<br>Scale Fidelity          |                       | ±0.05                    | ±0.10          | ±0.10                   |

| Drift of Test Set                                    |                       | ±0.10                    | ±0.10          | ±0.10                   |

| Output Connector Pair                                |                       | ±0.25                    | ±0.25          |                         |

| Input Connector Pair                                 |                       |                          | ±0.25          | ±0.25                   |

| Power Meter Scale                                    |                       | ±0.11                    | ±0.11          | ±0.10                   |

| Input Power                                          |                       |                          | ±0.05          | ±0.10                   |

| SSE Cancellation                                     |                       |                          |                | ±0.10                   |

| Polarization Controller/Filter<br>Path Loss          |                       |                          |                | ±0.07                   |

| Optical Spectrum Analyzer<br>Resolution Bandwidth    |                       |                          |                | ±0.10                   |

| Total Uncertainty:                                   | Connectors<br>Splices | ±0.39<br>±0.27           | ±0.48<br>±0.24 | ±0.39<br>±0.25          |

#### **Software**

Testing an EDFA device in production requires software that is easy to use, since EDFA measurement methods are quite new and the software will be used by people who may not know all of the details of the test process. On the other hand, software flexibility was an important design goal to allow extensions for additional measurement methods and integration into existing customer processes and databases.

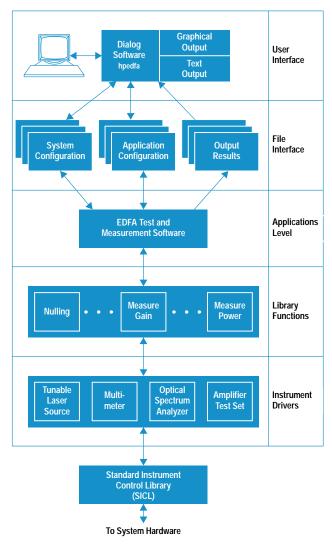

Fig. 6. EDFA test system software overview.

The EDFA test system software runs on an HP 745i work-station under the HP-UX\* 9.01 operating system, and is implemented mostly in the C programming language. Fig. 6 shows an overview of the software structure. On the lower level, there is a set of drivers for the different instruments, along with some modules for accessing configuration information and help texts. They supply an easy and portable access to the instrument hardware shown in Fig. 2.

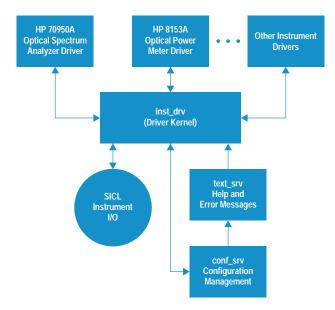

The communication layer for the instrument drivers is based on the SICL (Standard Instrument Control Library). Using the SICL, data can be written to and read from instruments with commands similar to those for reading and writing files in C. All calls to the SICL are handled through a control module called inst\_drv (Fig. 7). Its purpose is to allow the logging of traffic going to and from the instruments and to support some basic functionality like detecting the presence of an instrument on the HP-IB (IEEE 488, IEC 625). It also supplies central error handling facilities.

For each instrument type there is a separate driver module. Each module can control several instruments of the same type at once, and keeps track of the internal instrument states to save execution time. The driver modules check

parameters before passing them to the instruments, and support instrument error checking.

To speed up measurements where multiple instruments are involved, the drivers act asynchronously. For example, both channels of the HP 8153A optical power meter can fetch data while the HP 70950 optical spectrum analyzer is making a swept measurement. Additional commands are available to synchronize the instruments and make sure everything is settled before a measurement is taken.

The measurement application is built on top of this driver structure. It contains different algorithms for testing EDFAs, one of which is active at a time. Currently, the following measurement functions are integrated:

- Perform an input calibration of the test system

- · Perform an output calibration of the test system

- Verify the calibration

- Measure an EDFA using the polarization extinction method

- Measure an EDFA using the amplified spontaneous emission method

- Perform a self-test.

While the measurement proceeds, intermediate results are checked against limits set up for the device by the operator, and against certain fixed system limits (to detect improper connections, etc.).

A C language interface allows customized extensions, such as controlling additional parameters (e.g., the EDFA pump current) or performing additional measurements (e.g., reading a voltmeter).

All results of the calibration and measurement steps are stored in a single file, along with information about the EDFA device, the test conditions, and the overall result (pass or fail). This file is organized in a structured ASCII format and allows easy extraction of all important test results for use in analysis programs and databases.

For user-friendly parameter input and measurement control, a sophisticated user interface was designed. Written with a

Fig. 7. Instrument driver overview.

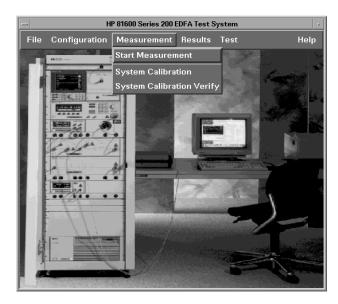

Fig. 8. Main window of the EDFA test system user interface.

user interface builder, along with some C code, it is based on X11/Motif (Fig. 8).

The user is guided through the setup and calibration of the test system by easy-to-use menus and dialog boxes. Different calibration setups for specific wavelength ranges can be entered, as well as test conditions with limits appropriate for certain EDFAs (Fig. 9).

Where fiber connections have to be made in the calibration and measurement process, a graphic is brought up on the screen showing the necessary steps and connections. All

Fig. 9. Test condition input panel.

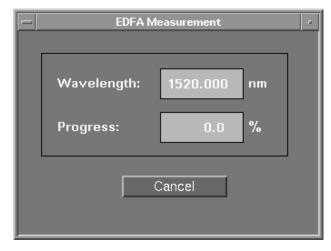

Fig. 10. Progress status window.

numeric data is checked for correctness immediately after it is entered. Before a measurement starts, the calibration is matched against the needs of the requested test.

The progress of a running calibration or test is shown with an information box on the screen (Fig. 10). Meanwhile, the program stays fully usable for entering new test setup data, or for reviewing the results of previous measurements.

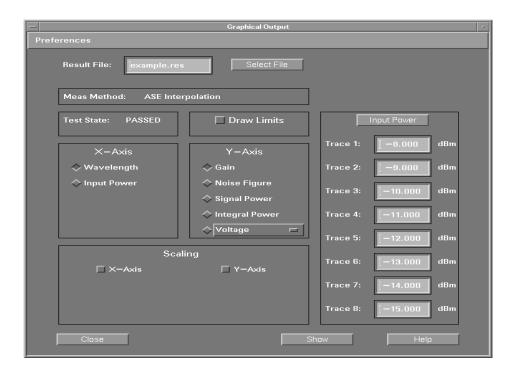

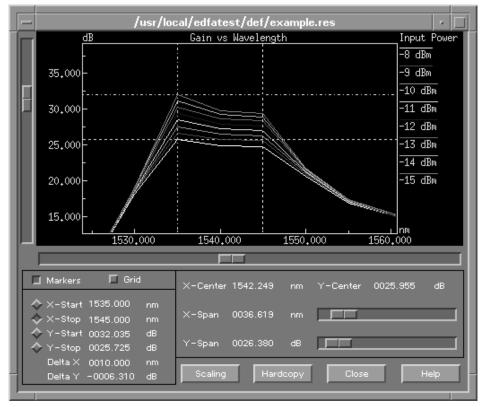

Result data can be examined in textual form. A table showing input parameters and results can be viewed and printed. A graphical output system is included so that the user can review the data graphically and create graphs for EDFA device documentation.

A menu (Fig. 11) allows the user to choose an X-Y plot of any result parameter against any input parameter (including user-specified parameters). Fig. 12 shows such a plot. A single graph can have up to eight traces. The graph can be interactively scaled and zoomed, and markers can be placed either freely or bound to measurement points. The X-Y values of each measurement point can be read out with a single mouse click.

The graphics system also provides hard-copy functionality and allows the merging of different graphs on a specified number of pages, thus enabling the output of a user-defined data sheet which can be printed out automatically after each test is completed. Supported printers are the HP LaserJet series and the DeskJet series, the latter allowing color printouts.

#### Acknowledgments

We wish to thank Bernd Maisenbacher for project management and Emmerich Müller for help in the development of the polarization controller and measurement technique. We also want to thank Robert Jahn who was responsible for implementing the measurement routines and coordinating all software related issues. In addition we also thank Wolfgang Reichert for the mechanical design of the polarization controller, amplifier test set, and rack. Wolfgang was also responsible for coordinating the development of the amplifier test set. Also, we want to thank our production engineers Jürgen Mang and Reinhard Becker for writing test software. Last not least, Doug Baney of HP Laboratories provided the scientific support and background. Finally we want to thank

Fig. 11. Graphical output window.

**Fig. 12.** X-Y parameter plot with markers.

Jack Dupre, Jim Stimple, Zoltan Azary, and Dave Baily at the Lightwave Operation for their support on optical spectrum analyzer related issues.

#### References

- 1. D. Baney, C. Hentschel, and J. Dupre, "Optical Fiber Amplifiers—Measurement of Gain and Noise Figure," *Hewlett-Packard Lightwave Symposium*, 1993.

- 2. C. Hentschel, E. Müller, and E. Leckel, "EDFA Noise Figure Measurements—Comparison between Optical and Electrical Techniques," *Hewlett-Packard Lightwave Symposium*, 1994.

- 3. *Hewlett-Packard Journal*, Vol. 44, no. 1, February 1993, pp. 11-38. 4. *Hewlett-Packard Journal*, Vol. 42, no. 1, February 1991, pp. 58-83.

HP-UX is based on and is compatible with Novell's UNIX® operating system. It also complies with X/Open's\* XPG4, POSIX 1003.1, 1003.2, FIPS 151-1, and SVID2 interface specifications. UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Limited.

X/Open is a trademark of X/Open Company Limited in the UK and other countries.

Motif is a trademark of the Open Software Foundation in the U.S.A. and other countries.

### Multi-Quantum-Well Ridge Waveguide Lasers for Tunable External-Cavity Sources

A new multi-quantum-well ridge waveguide laser enhanced for use in a grating-tuned external-cavity source has been developed. The device offers higher output power and wider tunability for improved performance in a new instrument. A core technology has been developed for use in a variety of light-emitting devices.

by Tirumala R. Ranganath, Michael J. Ludowise, Patricia A. Beck, Dennis J. Derickson, William H. Perez, Tim L. Bagwell, and David M. Braun

Tunable laser sources for testing of optical components and subsystems are an important part of a family of lightwave communication test and measurement instruments that HP has developed over the last decade. Currently, HP offers two tunable laser sources: the HP 8167A and HP 8168A. These instruments function in the wavelength windows centered at 1300 nm and 1550 nm.

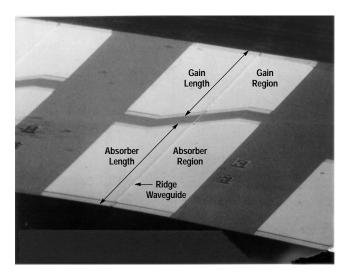

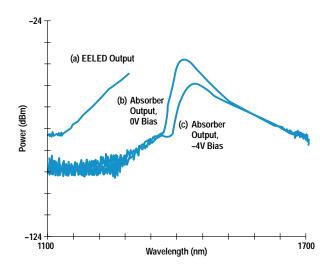

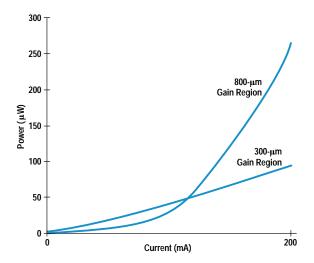

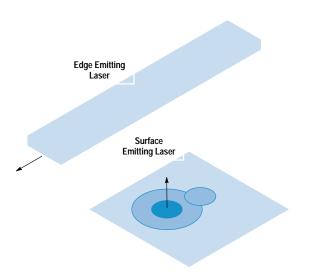

Custom requirements of test instruments cannot always be met by commercially available lasers. As a result, semiconductor laser development was begun to provide core material and device technologies that would produce suitable optical gain media chips for future tunable laser sources. The laser described in this article is the optical gain medium for the HP 8168C tunable laser source. The same technology forms the basis for other custom optical sources, such as the edge-emitting LEDs discussed in the article on page 43.

There are many different aspects to the development of a custom laser chip: device design, material growth, fabrication, testing, and reliability. Wide tunability and high output power are two very important requirements for the instrument application. The device must also be capable of operation in an external-cavity laser source like the HP 8168C.

A semiconductor laser is an optical oscillator, and like any oscillator, it consists of an optical amplifier (realized in a suitable semiconductor material system) together with feedback (provided by two atomically parallel cleaved facets). There are two classes of semiconductor lasers: gain guided and index guided. They are distinguished by the waveguiding mechanism for the optical field. Gain guided devices are relatively simple to fabricate but have high threshold current and astigmatism of the output beam. Index guided lasers can be more challenging to fabricate but offer low threshold currents, high linearity of output power, and good beam quality.

There are a number of variants of the index guided laser. The most sophisticated involve multiple regrowths of epitaxial material around the waveguide. A ridge waveguide laser,<sup>2</sup> while still index guided, has no regrowth steps, moderate threshold currents, excellent beam quality, and potentially

high reliability. Ridge structures do not exhibit the best linearity of output power with current drive (as do the best buried structures) and therefore are not suitable for applications such as CATV. But for external-cavity sources, ridge waveguide lasers provide excellent performance.

The amplifying region in the ridge structure allows a single optical mode to propagate while a suitable electron-hole population distribution is maintained by an electrical current. Details such as material composition, layer thickness, and ridge dimensions impact the threshold current, differential quantum efficiency, and far-field divergence angles of the light emanating from the two device facets. The far-field divergence angles determine how efficiently the device can couple to a hybrid grating-tuned external cavity on one side and to a single-mode fiber output on the other. The device threshold current is the point at which the amplifier gain equals the total cavity losses. Useful optical power output is obtained only for currents greater than threshold. Differential quantum efficiency is a measure of the device's ability to convert electrical energy to coherent optical output power, once the injected current exceeds threshold.

Tunability is intimately tied to the electronic band structure of the semiconductor as well as our ability to grow a device's light-emitting region by means of a vapor phase technique known as organometallic vapor phase epitaxy (OMVPE). To operate in an external cavity, a device also needs an antireflection coating. Devices must be reliable, so time-consuming reliability studies are done. Groups of devices are stressed at high temperatures, high currents, or both for many thousands of hours. Also, devices must be tested in chip form and in subassembly module form.<sup>3</sup> To anticipate instrument operation a laboratory grating-tuned external cavity is used. This allows a quick look at tunability and output power for a given device.

#### **Semiconductor Laser Device**

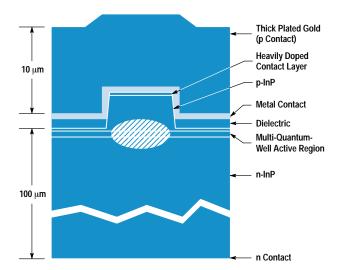

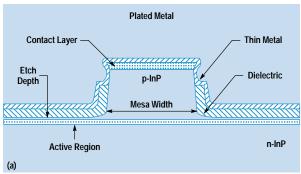

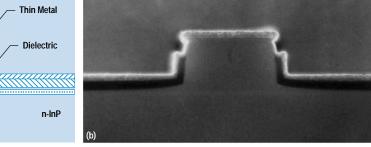

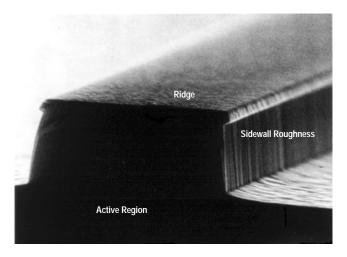

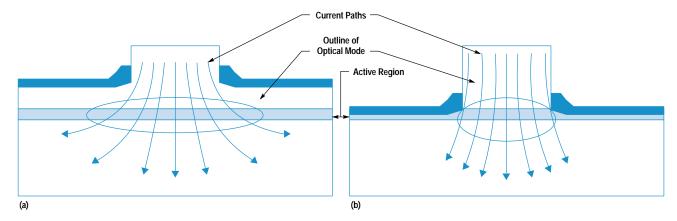

In Fig. 1 we show a schematic cross section of a ridge waveguide laser. Essential features of our device are a multiquantum-well active region surrounded by n-type and p-type

Fig. 1. Ridge waveguide laser cross section.

InP cladding regions. The upper part of the device has an etched ridge whose function it is to confine light laterally, forming a single-mode optical waveguide. With a p ohmic metal contact on the ridge top and an insulator on either side, current is confined to a specific region. The completed device has front and back facets cleaved to form atomically flat and parallel end mirrors. The two end mirrors together with the optical waveguide form an optical cavity. The ridge is typically a few micrometers wide and a few micrometers high, while the completed chip is on the order of 100 micrometers thick and a few hundred micrometers on each side. The p contact has a thick gold pad plated to act as a heat spreader in addition to forming a bond pad. An n contact on the backside of the chip completes the device.

#### **Active Region Design**

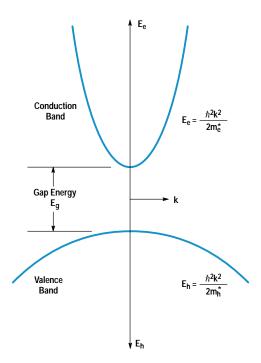

Absorption, Stimulated Emission, and Optical Gain. In a direct bandgap semiconductor (say, the active region of a laser), an electron from a filled valence band state can absorb an incident photon (of energy >  $E_g$ , where  $E_g$  is the bandgap energy). In the process the electron gets transferred to a conduction band state, leaving behind a vacancy (hole). The absorption rate depends on the incident photon flux and the density of available conduction band states. In the reverse process, stimulated emission, an incoming photon of energy E<sub>D</sub> stimulates an electron-hole pair to emit a second in-phase photon (of energy E<sub>p</sub>). The stimulated emission rate depends on the incident photon flux, the density of electrons in the conduction band, and the density of holes (at the correct energy) in the valence band. A quantum-mechanical matrix element that measures the strength of the optical coupling between hole states (in the valence band) and electron states (in the conduction band) enters into the calculation for optical absorption and emission states.

It is this stimulated emission process, under conditions of electrical pumping (with a sufficient density of electrons and holes in the conduction and valence band states) that can provide optical gain. When the stimulated emission rate exceeds the (stimulated) absorption rate there is net optical gain. This is generally possible only under high electrical pumping conditions. In addition, an electron from the conduction band can spontaneously emit a photon by recombining

**Fig. 2.** Parabolic energy E versus crystal momentum k diagram (simplified) for a direct bandgap semiconductor having an energy gap  $E_g$ . The difference in curvatures reflects the difference in carrier effective masses for electrons  $(m_e^*)$  and holes  $(m_h^*)$ .

with a hole from a valence band state. This process does not depend on the presence of an incident photon and gives rise to optical noise in laser devices.

**Electron/Hole Density of States and Tunability.** To gain an appreciation for how optical gain over a broad window arises, a brief examination of electron/hole states in a direct bandgap semiconductor is useful. In a bulk direct bandgap semiconductor, electron and hole states generally exhibit a parabolic relation between energy E and the crystal momentum k (see Fig. 2). In the conduction band,

$$E_{\rm e} = \frac{\hbar^2 k^2}{2m_{\rm e}^*},$$

where  $m_{\rm e}^*$  is the electron effective mass, and in the valence band.

$$E_h = \frac{\hbar^2 k^2}{2m_h^*},$$

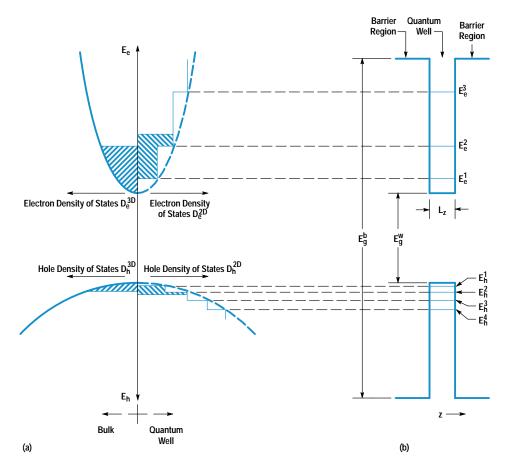

where  $m_h^*$  is the hole effective mass. The electron effective mass is about a factor of 10 smaller than the hole effective mass and this is reflected as a factor of 10 difference in the curvatures of the parabolas in the conduction and valence bands. The three-dimensional density of allowed electron and hole states per unit energy is proportional to  $\sqrt{E}$  for a bulk semiconductor. For the case of a very thin  $(L_Z\approx 10~\text{nm})$  layer of the same bulk semiconductor sandwiched between two barrier regions of a higher bandgap material, a structure known as a quantum well, the electron and hole motions are restricted and the allowed energies for motion normal to the layer are quantized and occur at discrete energies (say  $E_e^1$ ,  $E_e^2$ , ...) determined by the dimension  $L_Z$ . Motion in the plane of the film is not restricted and allowed energy states form a continuum. The result is a constant density of states for both

**Fig. 3.** (a) Parabolic and step density of states for bulk semiconductor (left of line) and quantum well (right of line). For a given volume density of carriers, electrons fill up to a greater depth for the quantum well case (right of line). (b) Discrete electron and hole energies from restricted z motion in a quantum well of thickness  $L_z$ . We have omitted the presence of a degenerate light hole band for this illustration.

electrons and holes.<sup>4</sup> Fig. 3 illustrates these observations for both bulk and quantum well semiconductor structures. Fig.3a shows (hatched regions) the same volume density of electrons (and holes) distributed in energy space for bulk (left of line) and quantum well (right of line) structures. The electrons fill up the available states and reach a higher energy for a quantum well than for a bulk active layer. It is this high energy state occupancy feature that allows a broad wavelength range of gain using quantum well active regions. Quantum well composition (which fixes the gap energy in the well region,  $E_g^{\text{W}}$ ) and thickness (Lz), together with barrier region composition (which fixes the gap energy in the barrier region,  $E_{g}^{b}$ ) determine the positions of the discrete levels  $E_e^1$ ,  $E_e^2$ , ... (see Fig. 3b). Level  $E_e^1$  determines the long-wavelength end of the gain spectrum. The short-wavelength (or higher-energy) end of the gain spectrum is determined by the loss of electron confinement in the quantum wells. This loss of electron confinement is primarily determined by the barrier energy gap E<sub>g</sub><sup>b</sup>. The upshot is that one needs to pick carefully the barrier material (for  $E_g^b$ ), the quantum well material (for E<sup>W</sup><sub>g</sub>), and the thickness L<sub>z</sub> to ensure a properly wavelength-centered and sufficiently broad gain spectrum to fit the instrument need. In practice, the modal gain provided by a single quantum well is quite modest, so multiple quantum wells are used in parallel to achieve the requisite gain.

#### **OMVPE Growth**

Organometallic vapor phase epitaxy (OMVPE) dominates contemporary production of the quaternary compound semi-conductor GaInAsP because of its relative simplicity, high yields, and scalability to large-area production. The GaInAsP material system has been studied since the early seventies

when it was realized that compositions lattice-matched to InP substrates would produce devices important for the then-incipient fiber-optic communication systems. OMVPE uses group III organometallic compounds such as triethylgallium (TEGa) or trimethylindium (TMIn, both metal alkyls) and hydrides of the group V elements, such as AsH<sub>3</sub> and PH<sub>3</sub>, as source materials for the vapor deposition. Vapors of the metal alkyls are entrained in a carrier gas, usually hydrogen, and transported to the heated substrate. The organometallics readily crack into single metal atoms and ethane or methane chains. The metal deposits on the growing surface, and the hydrocarbon chains are swept away in the carrier stream. Similarly, the hydrides also crack thermally, depositing only the group V atoms. A nearly perfect 1:1 stoichiometry of group V to group III atoms is achieved in the solid because the crystal strongly rejects excess group V atoms, which are volatile enough to evaporate.

The deposition zone design must incorporate several critical requirements. The substrate temperature must be uniform and tightly controlled since the As/P solid ratio is highly temperature-sensitive. The fluid dynamics must be controlled to deliver uniform amounts of precursor chemical to all parts of the substrate, and to compensate for any downstream depletion. Finally, turbulent flow streams defeat abrupt gas composition changes injected by the precision gas switching manifold and must be designed out. The laser diodes for the tunable source require precise control of the composition, thickness, and interfaces of nearly 20 epitaxial layers. The ratios of the four main gas constituents control the epitaxial GaInAsP composition, and the total metal alkyl concentration determines the epitaxial growth rate. Abrupt changes in

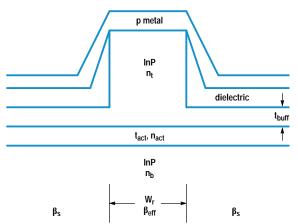

Want Small ( $\Theta_{\perp}$  and  $\Theta_{\parallel}$ ),  $I_{th}$ , and High  $\eta_d$

#### Optical Design

- 1.  $\,t_{act},\,n_{act},$  and  $n_t$  determine  $\beta_{eff}$  and  $\Theta_{\,\perp}\,.$

- 2.  $t_{buff}\,determines\,\beta_{S}.$

- 3.  $\beta_{eff}$ ,  $\beta_{s}$ , and  $W_{r}$  Determine  $\Theta_{\parallel}$ .

#### **Electrical Design**

- 1. Want t<sub>buff</sub> thin for small l<sub>th</sub>

- 2. If  $t_{buff} = 0$ , optical loss is high,  $l_{th}$  increases,  $\eta_d$  decreases.

- 3. Free-carrier plasma causes lateral optical spread and reduces  $\eta_d$  at high currents.

**Fig. 4.** Ridge waveguide laser design issues.  $\beta_{eff}$  and  $\beta_s$  are the optical propagation constants for equivalent slab waveguides whose layers are the same as in the ridge and side regions of the device, respectively.

composition are achieved by rapidly switching the gas composition. Slow variations in the metal alkyl vapor ratios and hydride gas flow produce gradually graded material. In all cases, the epitaxial layer must remain lattice-matched to the InP substrate to within 2 parts in  $10^4$  to suppress dislocation formation. This requires precise control over the alkyl temperature ( $\leq 0.1^{\circ}\text{C}$  variation), carrier gas flow, and the system pressure at several points.

The use of TMIn introduces another control complication. Unlike other commonly used metal alkyls, which are liquid over practical temperature ranges, TMIn is a solid. The concentration of the TMIn vapor sublimed into the gas stream varies (often unpredictably) with the solid surface area and the source lifetime. The TMIn vapor concentration in the hydrogen carrier gas must be constantly measured and controlled throughout the deposition cycle. By timing the transit of an ultrasound pulse through a real-time sample of the TMIn-hydrogen mixture, TMIn concentration to within 1 part in  $10^5$  can be determined.

Finally, small interfacial composition transients generate massive dislocation networks that destroy device performance. By controlling the temperatures, pressures, flows, and gas switching timings, essentially perfect interfaces can be formed. This allows growth of quaternary quantum wells as thin as 25Å.

#### Ridge Laser Design Issues

The final device requires relatively small far-field divergence angles ( $\Theta_{\perp}$  and  $\Theta_{\parallel}$ ), a small value of  $I_{th}$  and a high value for the differential quantum efficiency ( $\eta_d$ ). Thickness ( $t_{act}$ ) and effective index (n<sub>act</sub>) of the active layer together with the refractive indexes of the top (nt) and bottom (nb) buffer regions determine  $\beta_{eff}$  and in turn control the angle  $\Theta_{\perp}$  (see Fig. 4). (β<sub>eff</sub> is the optical propagation constant for an equivalent slab waveguide whose layers are the same as the ridge part of the device.) The thickness (t<sub>buff</sub>) of the buffer layer in the field and the width of the ridge (W<sub>r</sub>) determine the angle  $\Theta_{\parallel}$ . The thickness (t<sub>buff</sub>) determines the size of the index discontinuity between the ridge and the field. A low threshold current is achieved by minimizing waste of carriers (to unnecessary lateral current spreading into the field regions) and by shielding the optical field from metal losses by a sufficiently thick dielectric layer. By judicious choice of dimensions these efficiency degrading current spreading effects can be minimized to obtain an extremely reliable device.

Once threshold (sufficient gain to account for all losses) is reached, any extra current produces lasing photons. These photons still face losses from various physical mechanisms: absorption in pumped and unpumped regions, scattering from defects, metal absorption losses, and useful light output from the end mirrors. The differential quantum efficiency can be expressed as:

$$\eta_d \, = \, \eta_i \! \bigg( \! \frac{\alpha_{mir}}{\alpha_{mir} \, + \, \alpha_{int}} \! \bigg) \! , \label{eq:etadaction}$$

where  $\eta_i$  is the internal quantum efficiency indicating the fraction of injected carriers converted to photons,  $\alpha_{mir}$  is the loss resulting from light emitted from an end mirror, and  $\alpha_{int}$  is the loss resulting from various internal factors. Both non-radiative recombination at surfaces and defects and Auger recombination† make  $\eta_i$  less than 100%. Since  $\alpha_{mir}$  signifies useful output, one needs to keep  $\alpha_{int}$  to a tolerable minimum to achieve a high  $\eta_d$ . For a semiconductor laser of length  $L_d$  and facet reflectivity R,

$$\alpha_{\min} = (1/L_d) \ln(1/R).$$

A value of  $L_d$  chosen to make  $\alpha_{mir} = \alpha_{int}$  maximizes the output power. Factors dictated by instrument operation determine the actual device length.

#### **Device Fabrication and Testing**

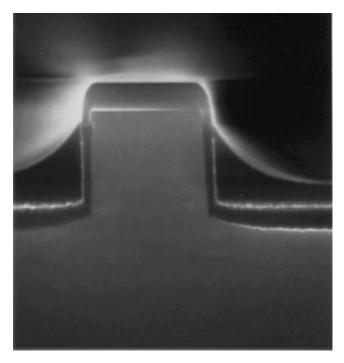

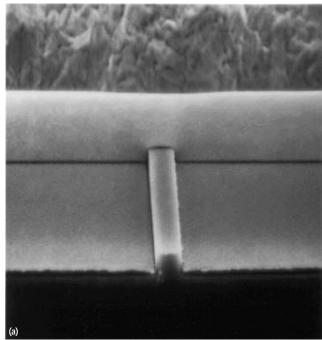

Starting with a proper structure epitaxially grown on n-type InP substrate, a mask for the ridge is defined photolithographically. Using this mask, ridges of the chosen width and height are etched using a methane/hydrogen reactive ion etch.<sup>6</sup> A dielectric layer is deposited all over and selectively cleared from the ridge tops using a self-aligned photoresist process. Fig. 5 is an SEM cross-section showing photoresist on the sides, selectively protecting the dielectric layer that covers the entire top surface. Following this step, the dielectric layer is etched off the ridge top and the photoresist is removed from the field (see Fig. 6). A p contact/metal combination is deposited, covering the exposed ridge tops and the dielectric in the field. A thick gold pad is plated over the p metals to act as a heat spreader and as a bond pad. The wafer is thinned and an n contact metallization is deposited. Following a high-temperature contact alloying step the wafer

<sup>†</sup> Very briefly, Auger recombination  $^5$  is a nonradiative and therefore lossy process that involves four particles: either three electrons and one hole or three holes and one electron. The Auger process is especially important in determining the temperature dependence of threshold current and  $\eta_i$  in long-wavelength semiconductor lasers such as ours.

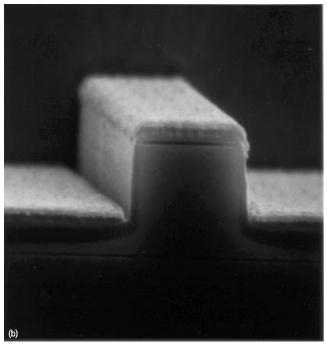

**Fig. 5.** Scanning electron microscope cross section of a ridge waveguide laser after exposure of ridge top with photoresist covering the oxide in the field.

is cleaved into bars for device testing. Fig. 7a is an SEM section of a completed device showing the ridge, a device facet, and the plated gold pad on top. Fig. 7b shows details of the device cross section with the active and contact layers clearly delineated.

Devices are first pulse tested in bar form to get an idea of their operation before die-attachment onto a heat sink. Devices 500 micrometers long have typical thresholds in the

**Fig. 6.** SEM cross section of a ridge waveguide laser after removal of the dielectric from the ridge top and photoresist from the field.

**Fig. 7.** (a) SEM section of a completed ridge laser showing the ridge and the plated gold. (b) SEM section of a ridge laser facet delineating the active and contact layers.

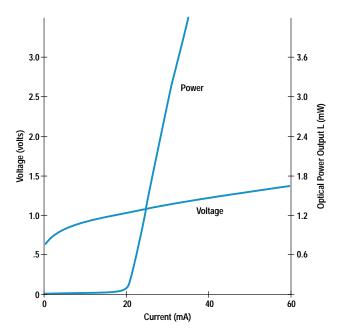

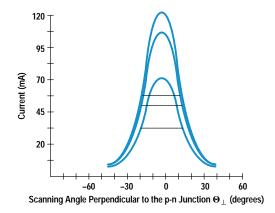

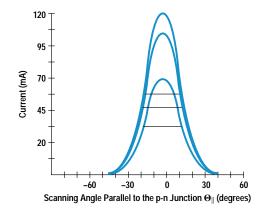

low 20-mA range with excellent slope efficiency and low divergence angles. Fig. 8 shows pulsed L-I and I-V characteristics, where L is light power output. Fig. 9 shows the far-field divergence angles perpendicular  $(\Theta_{\perp})$  and parallel  $(\Theta_{\parallel})$  to the plane of the device at different currents.

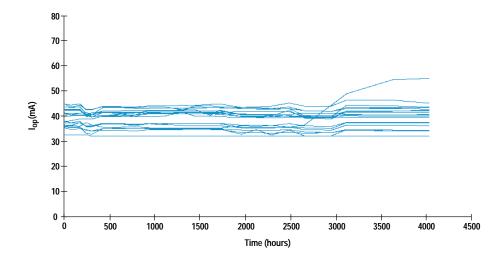

#### **Device Reliability**

A number of factors go into ensuring the reliability of our devices. To project device lifetimes under operational conditions, batches of devices die-attached to a suitable heat sink are subjected to elevated temperatures and a high bias current over many thousand hours. Periodically threshold

**Fig. 8.** Pulsed L-I (optical power output versus current) and I-V curves for a representative 1550-nm ridge waveguide laser.

current, power, and differential quantum efficiency are measured. The change in these parameters for devices stressed at different temperatures can be used to extract an activation energy for the principal failure mechanism. Device lifetime can then be predicted for normal operating conditions.

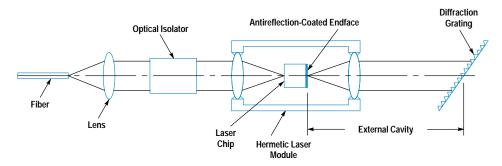

#### **External-Cavity Operation**

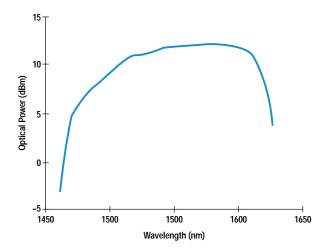

Completed individual devices are mounted on a heat sink. One facet is antireflection coated with a broadband multi-layer coating.<sup>3</sup> The quality of this coating determines the suppression level of output power variations (from parasitic reflections), and  $\leq 1$  dB at the highest power levels of operation is achievable. With one of these devices properly aligned in an external cavity (see Fig. 10) we can generate a wavelength tuning curve at any operating current. Fig. 11 shows the power output as a function of wavelength for a representative device tested in an external cavity at an operating current of  $\approx 120$  mA.

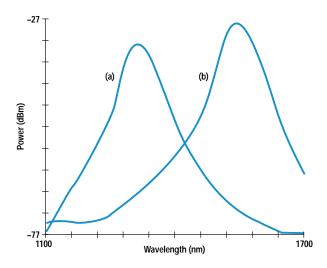

Devices show >0 dBm output power (in a collimated beam) over the wavelength window 1465 to 1625 nm and put out >10 dBm over a smaller window, 1505 to 1615 nm. A single-mode fiber provides the output of the instrument (HP 8168C). With a reflection suppressing isolator included, these raw power output and tuning numbers are degraded somewhat.

| Peak Current<br>(mA) | $\Theta_{\perp}$ FWHM (Degrees) |

|----------------------|---------------------------------|

| 70                   | 32.6                            |

| 100                  | 32.7                            |

| 120                  | 32.7                            |

| Peak Current<br>(mA) | $\Theta_{  }$ FWHM (Degrees) |

|----------------------|------------------------------|

| 70                   | 23.4                         |

| 100                  | 23.5                         |

| 120                  | 23.9                         |

Fig. 9. Far-field divergence angles perpendicular  $(\Theta_\perp)$  and parallel  $(\Theta_\parallel)$  to the device junction plane.

Nevertheless, these new custom ridge waveguide laser chips still provide significant increases in the power output and tuning window for the new instrument. The HP 8168C covers the range 1470 to 1590 nm with power increased by 8 dB and tuning window widened by a factor of two over the HP 8168A. Offering higher power (+2.5 dBm) in the range 1520

**Fig. 10.** Schematic of a laboratory grating-tuned external-cavity test setup.

**Fig. 11.** Power output as a function of wavelength for a representative ridge laser in an external cavity.

to 1565 nm, this instrument is expected to be very useful for saturation measurements of erbium-doped fiber amplifier (EDFA) systems.

#### **Summary**

26

A multi-quantum-well ridge waveguide laser enhanced for use in a grating-tuned external-cavity source has been developed. The device offers higher output power and wider tunability in the new HP 8168C tunable laser source. This tunable optical source will allow simple testing of components for wavelength division multiplexing (WDM) as well as complete testing of EDFA systems. The core technology will allow the

fabrication of other custom light sources in the wavelength window 1200 to 1700 nm.

#### Acknowledgments

The authors would specially like to thank Rose Twist for assistance in process development and device fabrication and Pamela Langhoff for assistance with epitaxial growth. Other people who have contributed to this project include: Jean Norman, Gary Trott, Joan Henderson, Mimi Planting, Nance Andring, Kari Salomaa, Nancy Wandrey, Deborah Sowers, and Roger Jungerman. We would like to express our appreciation for managerial support from Rick Trutna, Waguih Ishak, Kent Carey, Susan Sloan, Bob Bray, Jun Amano, and Ron Moon.

#### References

- 1. B. Maisenbacher, E. Leckel, R. Jahn, and M. Pott, "Tunable Laser Sources for Optical Amplifier Testing," *Hewlett-Packard Journal*, Vol. 44, no. 1, February 1993, pp. 11-19.

- 2. I.P. Kaminow, R.E. Nahory, M.A. Pollack, L.W. Stulz, and J.C. Dewinter, "Single-mode CW ridge-waveguide laser emitting at 1.55 µm," *Electronics Letters*, Vol. 15, 1979, pp. 763-765.

- 3. R.L. Jungerman, D.M. Braun, and K.K. Salomaa, "Dual-Output Laser Module for a Tunable Laser Source," *Hewlett-Packard Journal*, Vol. 44, no. 1, February 1993, pp. 32-34.

- 4. C. Weisbuch and B. Vinter, *Quantum Semiconductor Structures*, Academic Press, 1991, p. 21.

- 5. G.P. Agrawal and N.K. Dutta, *Long-Wavelength Semiconductor Lasers*, Van Nostrand Reinhold, 1986, Chapter 3.

- 6. U. Niggebrugge, M. Klug, and G. Garus, "A novel process for reactive ion etching on InP, using CH<sub>4</sub>/H<sub>2</sub>," *Institute of Physics Conference Series*, no. 79, 1986, pp. 367-372.

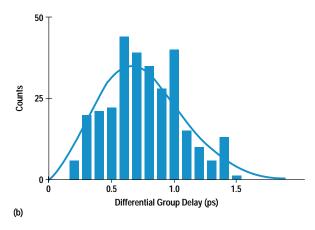

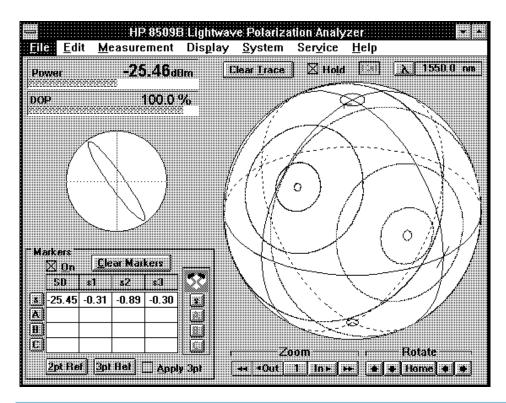

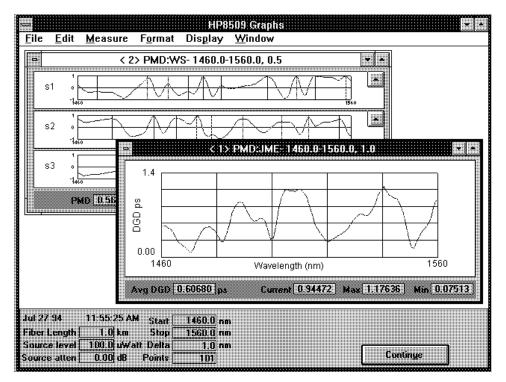

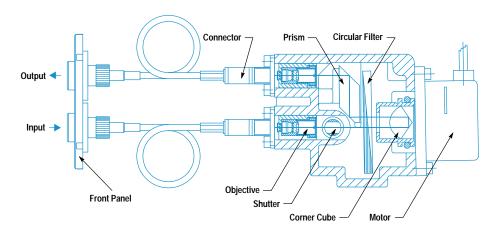

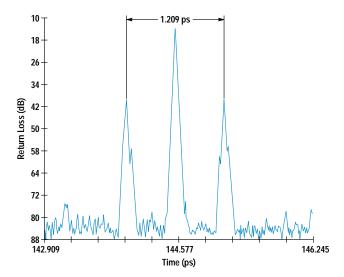

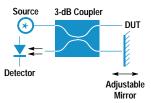

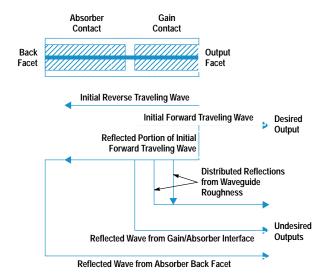

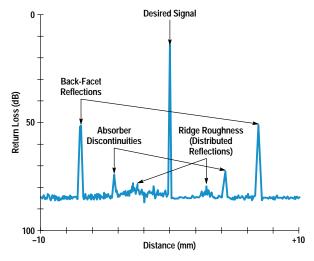

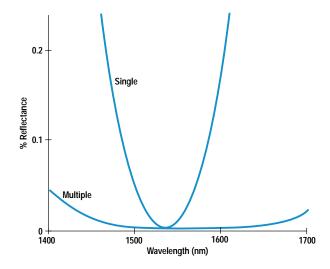

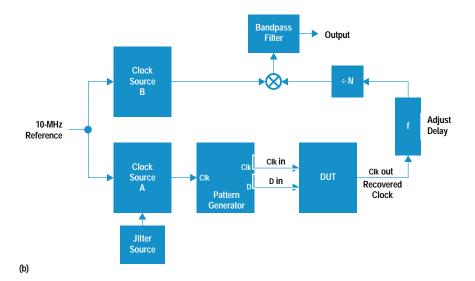

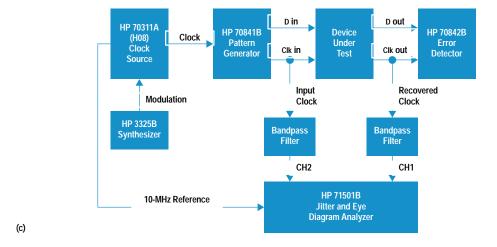

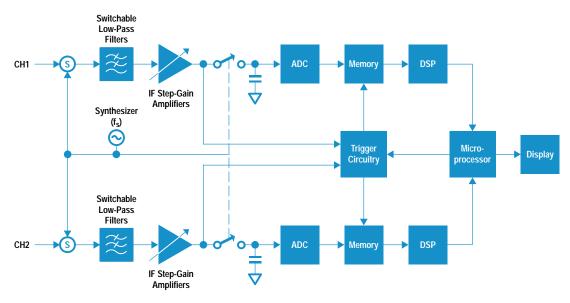

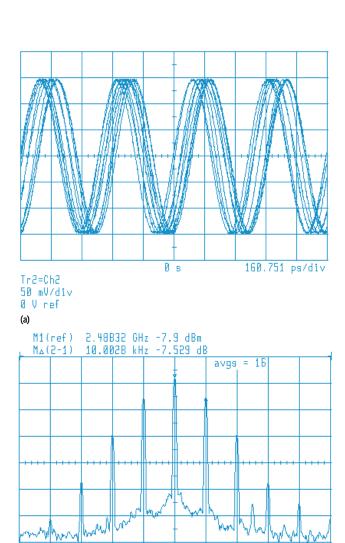

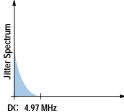

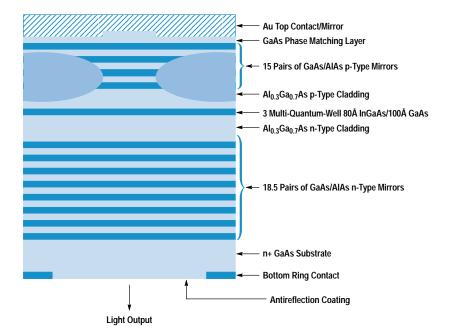

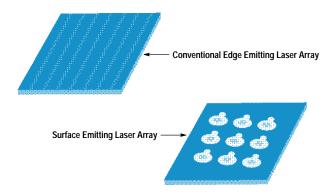

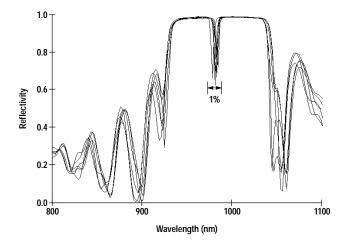

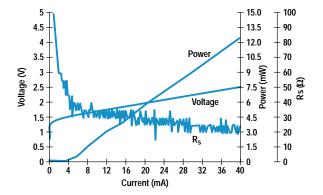

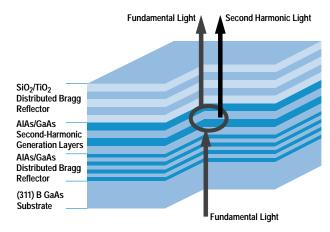

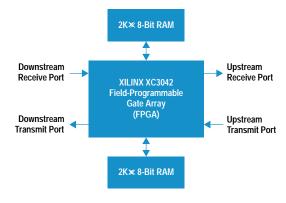

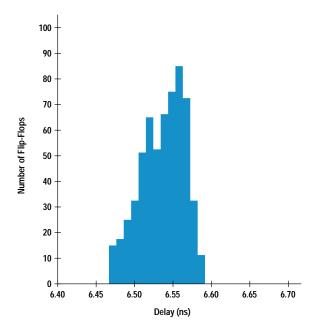

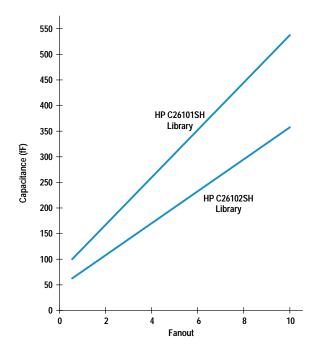

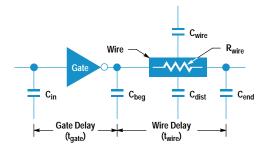

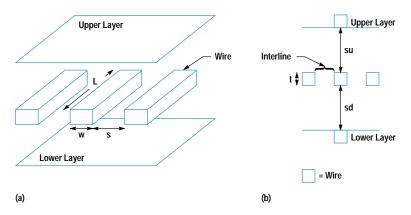

February 1995 Hewlett-Packard Journal © Hewlett-Packard Company 1995